流水线的概念

基本定义:把一个重复的过程分解为若干个子过程,每个子过程由专门的功能部件实现。把多个处理过程在时间上错开,依次通过个功能段,每个子过程可以与其他子过程并行处理。

流水线的段(级):流水线中每个子过程及其功能部件。

流水线的深度:流水线的段数。

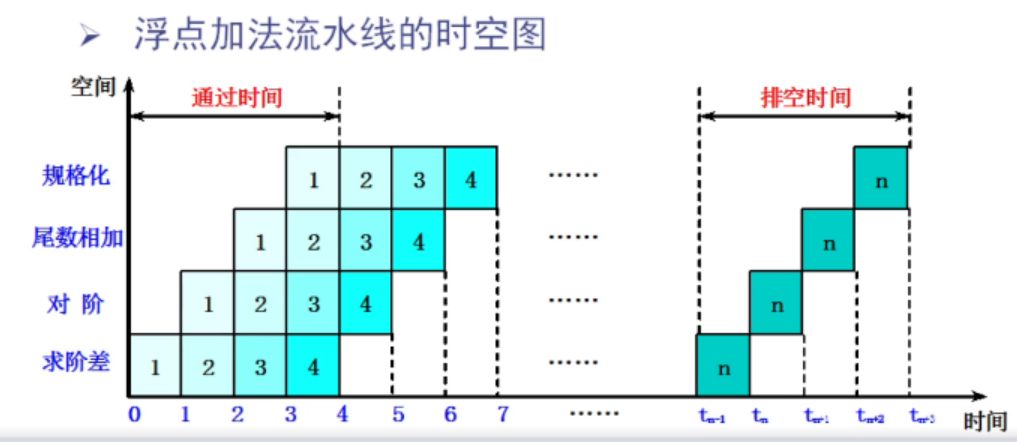

流水线的通过时间和排空时间

通过时间

第一个任务从开始到结束的时间。

排空时间

最后一个任务n开始到结束时间

流水线的性能指标

吞吐率TP

单位时间内流水线所完成的任务数量或输出结果的数量。

TP=n/Tk

n:任务数

Tk:处理n个任务所用时间

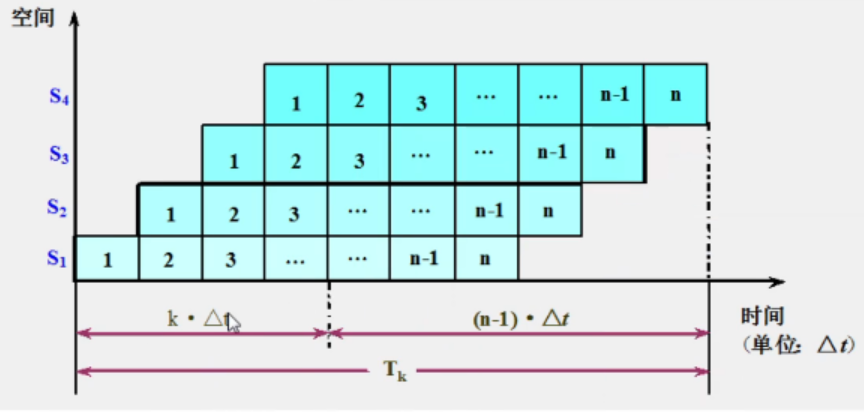

各段时间相等的流水线

Tk=k△t+(n-1)△t

TP=n/(k△t+(n-1)△t)

最大吞吐率为n趋近于∞时,TPmax=1/△t

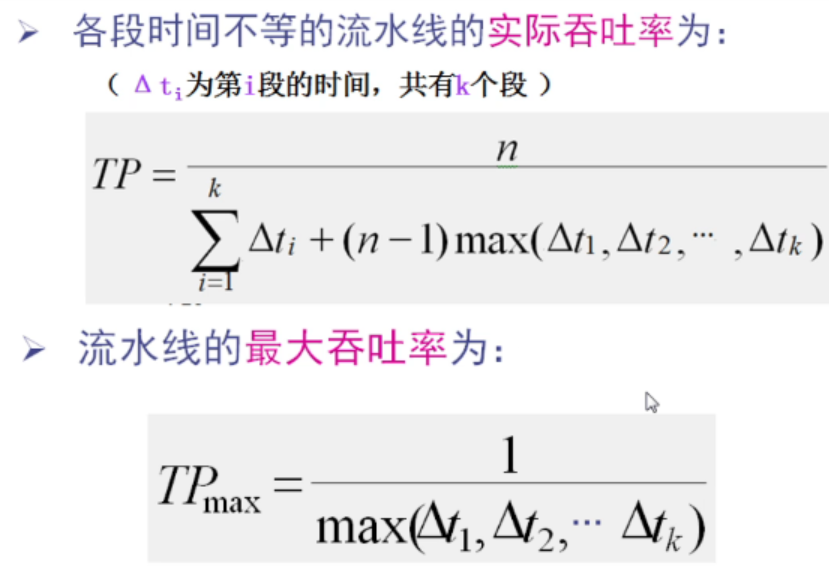

各段时间不完全相等的流水线

流水线中时间最长的段被称为流水线的瓶颈段。

因此对于瓶颈段,多要采用分割,分为多个子流水段,或者增加处理硬件。

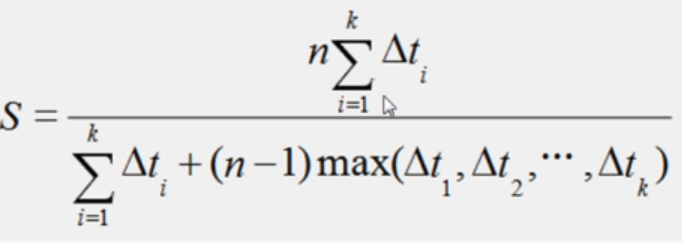

加速比S

完成同一批任务,不使用流水线的时间(Ts)和使用流水线的时间(Tk)之比。

S=Ts/Tk

各段时间相等的流水线

S=nk△t/(k△t+(n-1)△t)=nk/(k+n-1)

n趋于∞时Smax=k

各段时间不完全相等的流水线

流水线的效率

流水线中设备实际使用时间:整个运行时间的比值,也就是利用率。

各段时间相等的流水线

e1=e2=…=ek=n/(k+n-1)

整条流水线效率为:E=(e1+e2+…ek)/k=n/(k+n-1)

Emax=1

在图像上,流水线效率=流水线面积/总面积

流水线设计中的三个问题:

颈问题:

机器时钟周期取决于瓶颈段的延迟时间。设计时应该使各段时间相等

流水线的额外开销:

- 流水寄存器需要建立时间和传输延迟

- 时钟偏移开销

冲突问题

- 运算操作的数据准备

- 指令操作的相互关联

五段流水线

取指令周期 IF

- 从PC取出指令放到IR

- PC+=4

指令译码/读寄存器周期 ID

- 译码,读出操作数

执行/有效地址计算周期 EX

- 计算有效地址

存储器访问/分支完成周期 MEM

- 只有load,store和分支指令,其他类型指令不做任何操作。

写回周期 WB

- ALU运算指令和load指令把结果数据写入通用寄存器组。

相关

两条指令之间存在某种依赖关系。

数据相关:

两条指令i和j如果存在:

- j使用i产生的结果

- 指令j与指令k数据相关,而k又和i数据相关。(传递性)

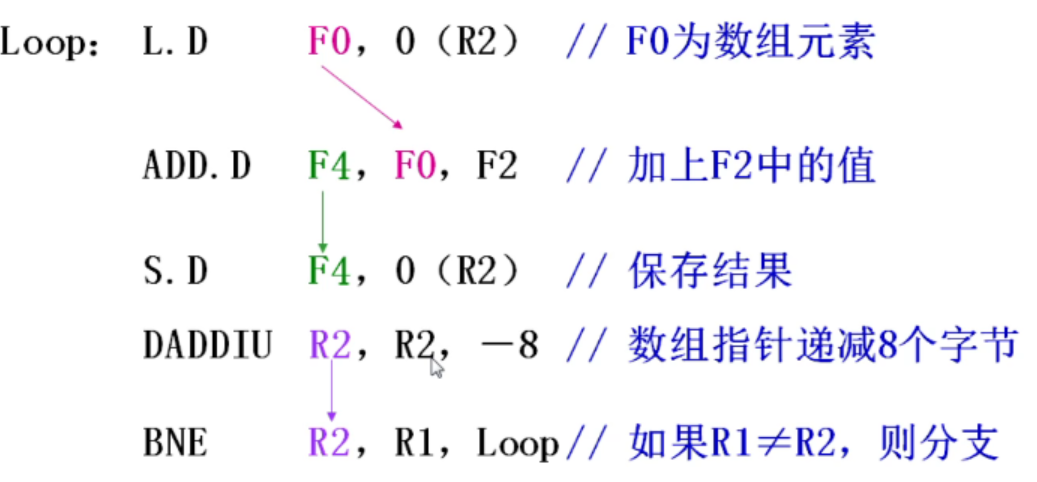

例如:

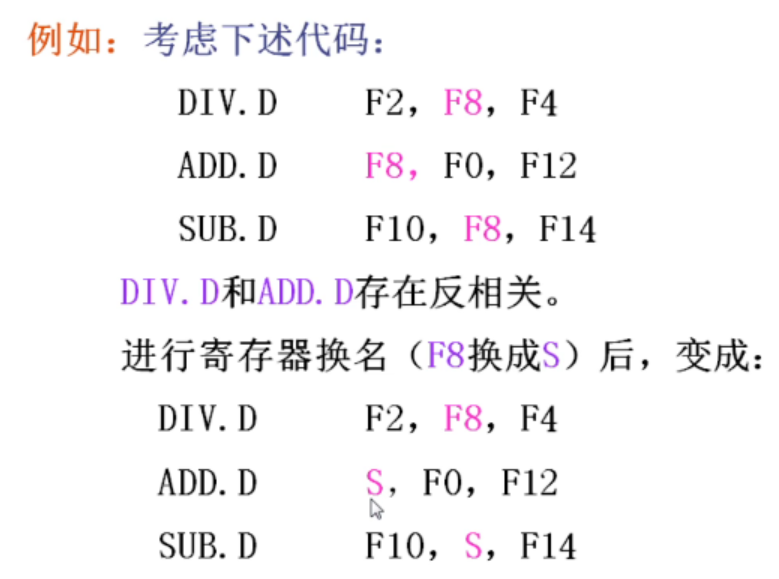

名相关

名:指令所访问的寄存器或存储器单元的名称

指令i,j之间:

反相关:指令J写的名=指令I读的名

输出相关:指令J写的名=指令I写的名

控制相关

是由分支指令引起的相关。

例如if-then语句

if p1{

S1;

}

S;

if p2{

S2;

}

P1与S1存在控制相关,P2与S2存在控制相关

冲突

结构冲突:

硬件资源不满足指令执行要求

数据冲突:

需要用到前面的指令执行结果

指令I和J,I在J前进入流水线。

写后读冲突RAW

i写入前j先读(数据相关)

写后写冲突WAW

i写入前j先写(输出相关)

读后写冲突WAR

i读入前j先写(反相关)

控制冲突:

遇到分支指令和其他会改变PC值的指令

解决冲突的方法

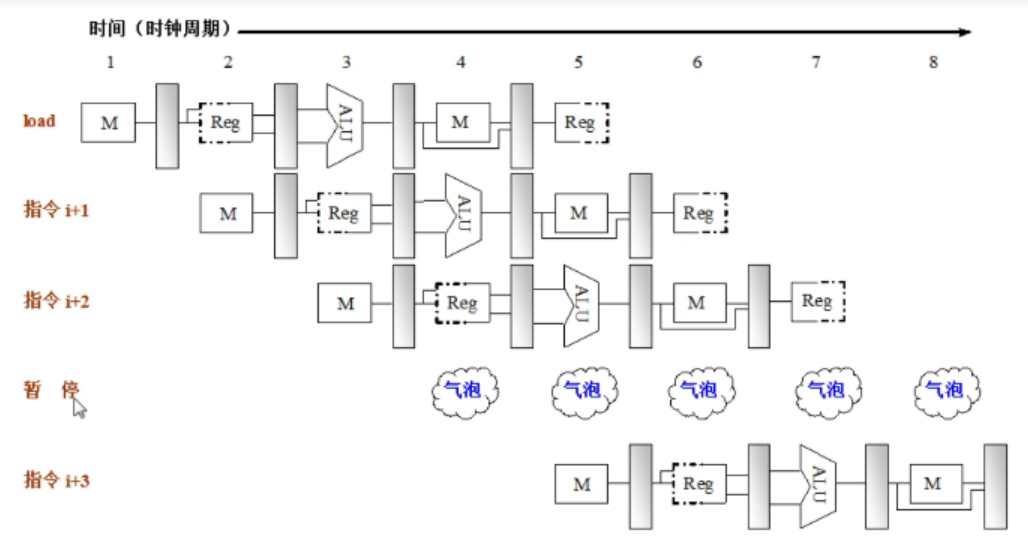

指令被暂停时,该暂停指令之后流出的所有指令都要暂停,之前的继续执行

结构冲突

访存冲突:只有一个存储器时,数据指令都要读取。

方法1:插入气泡

方法2:设置独立指令Cache和数据Cache

数据冲突

定向技术减少写后读冲突(数据相关):EX段和MEM段之间的流水寄存器保存的ALU计算结果总是回送到ALU入口,当检测到需要用前一个ALU运算结果,就用保存在流水寄存器的值运算。

需要停顿的数据冲突:当定向技术无法解决,需要暂停流水线直到冲突消失

编译器解决数据冲突:通过编译器重新组织顺序。

控制冲突

冻结或者排空流水线,优点:简单。

分支指令引起的延迟叫分支延迟。

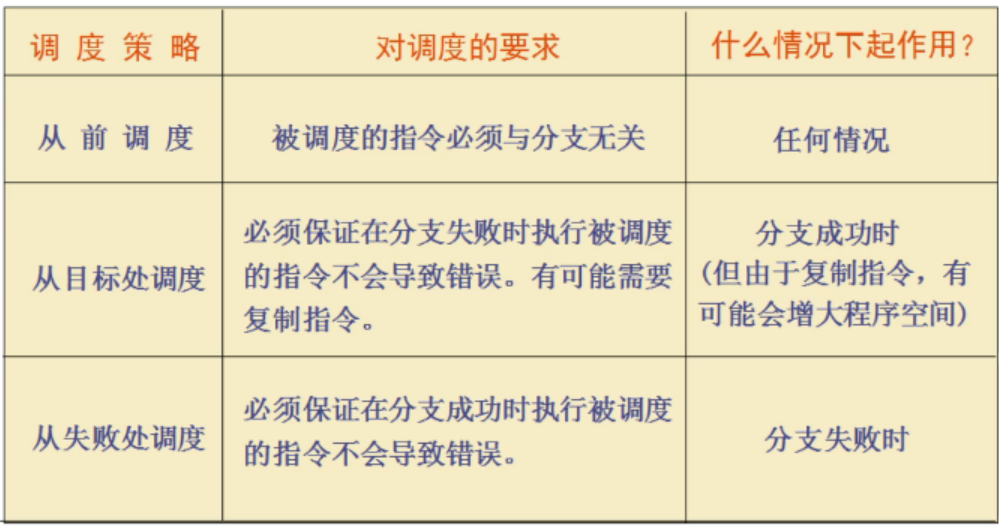

编译器减少分支延迟。预测分支失败,预测分支成功,延迟分支(插入延迟槽)。

延迟槽调度:

分支取消机制:

Q.E.D.